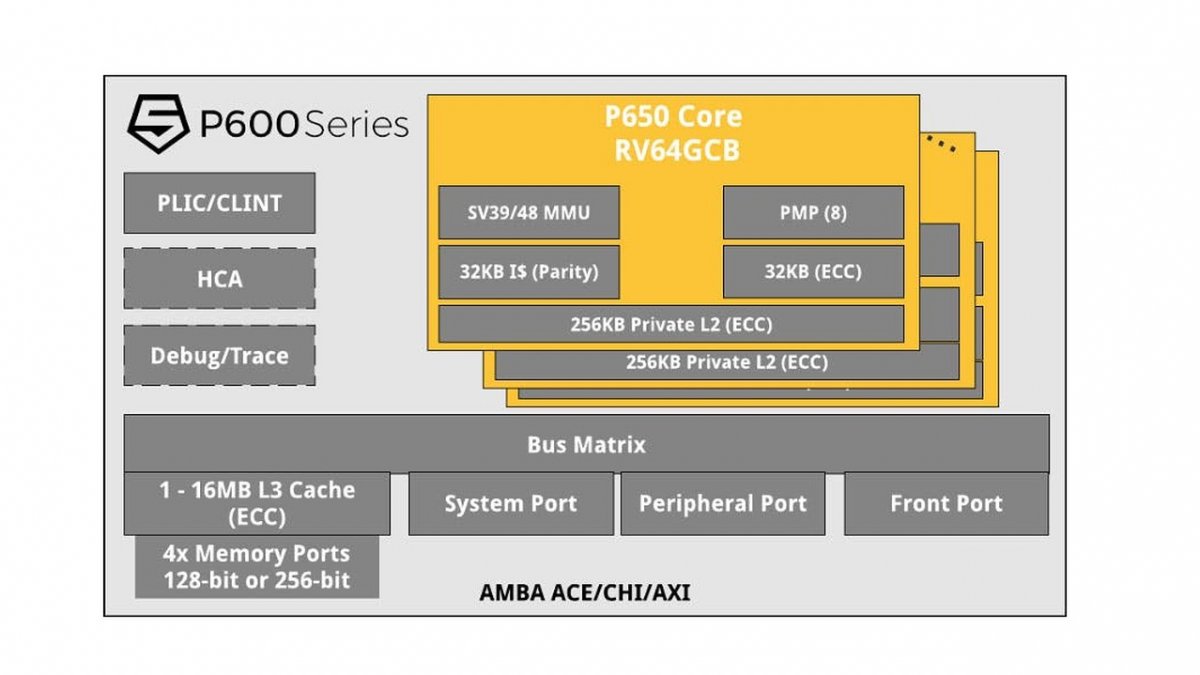

According to the developer SiFive, the Performance P650 is the most powerful processor core to date with the RISC-V instruction set architecture. In one to two years it could be used in Linux-compatible processors with up to 16 CPU cores, 16 MB L3 cache and numerous memory channels. Each core has a 64 KByte L1 cache (32 each for data and commands) and 256 KByte L2 cache. The computing power per cycle should be comparable to that of the ARM Cortex-A77 announced in 2019.

Areas of application for SoCs with P650 core SiFive sees in servers, vehicles and mobile devices, among other things. The SiFive Performance P650 meets the RISC-V specification RV64GCB as well as new specifications for hypervisor and virtualization approved by the RISC-V Foundation.

15 new RISC-V specifications

A few days before the RISC-V Summit in San Francisco, the members of the RISC-V Foundation ratified 15 specifications that describe a total of 40 extensions to the RISC-V-ISA. As mentioned, this includes virtualization functions, but also vector commands and those for scalar cryptography. The current versions of the RISC-V specifications can be found on GitHub.

Work in Progress

Like SiFive, it is also located in Silicon Valley, namely very close to the Intel headquarters in Santa Clara Rivos company that is still in stealth fashion economizes. Some top-class CPU experts who have already worked for companies like PA Semi are probably working there on a RISC-V chip for servers. Rivos is already a member of the RISC-V-Foundation and has secured the PCI-ID 7933 (0x1EFD).

In other places the teething troubles of the RISC-V technology become visible. So needs the RISC-V-SoC StarFive JH7100 special Linux patches for DMA access from I / O controllersbecause the chip does not itself take care of cache coherence. Similar Restrictions apply to the Allwinner D1 with the RV64GC core XuanTie C906.

- Podcast bit noise on the topic of RISC-V:

(queue)

– .